27.Q6b: 有限状态机次态逻辑

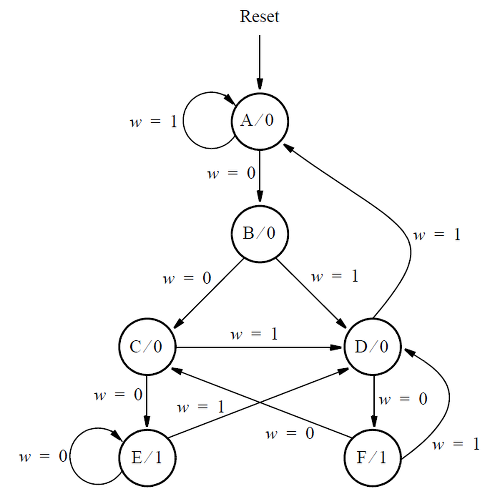

考虑下图所示的状态机,它有一个输入w和一个输出z。

假设你希望使用三个触发器来实现这个FSM(有限状态机),并且状态码y[3:1] = 000, 001, ... , 101分别代表状态A、B、...、F。为此FSM展示一个状态赋值表。推导出触发器y[2]的次态表达式。

仅实现y[2]的次态逻辑。(这个问题更多是关于FSM而非Verilog编码的问题。)

模块声明

module top_module (

input [3:1] y,

input w,

output Y2);